芯片简介:

74HC595集成芯片是一款能够实现串行输入、并行输出的移位寄存器,其内部含有8个移位寄存器,以及与其相对应的8个存储寄存器(输出端口支持三态输出),能够通过串行输出方式控制下一级级联芯片。

74HC595N芯片实物图

数据端引脚

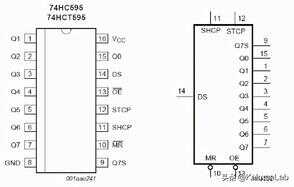

74HC595引脚图&逻辑符号

- Q0~Q7:8位并行输出引脚

- Q7S:级联用串行输出引脚

- DS:数据串行输入引脚

在进行芯片级联时,DS引脚接上一级芯片的Q7S引脚

控制端引脚

- MR:移位寄存器复位端

- SHCP:移位寄存器时钟输入引脚

- STCP:存储寄存器时钟输入引脚

- OE:输出端使能引脚

MR:低电平时,移位寄存器数据清零;

SHCP:上升沿时,移位寄存器数据移位,下降沿时,数据不变;

STCP:上升沿时,移位寄存器数据进入存储寄存器,下降沿时,数据不变;

OE:低电平使能,高电平时,Q1~Q7禁止输出(呈高阻态)。亦即,控制该引脚可轻松实现Q1~Q7引脚的0/1信号交替输出。

工作原理

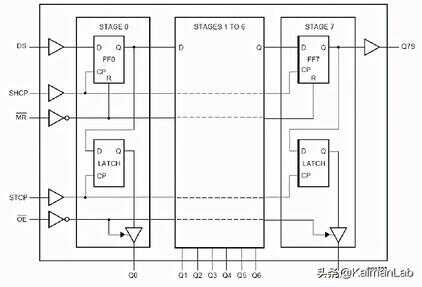

74HC595内部逻辑图

上图中FF0~FF7:8个移位寄存器,其正下方对应的为8个存储寄存器

如上图所示,移位寄存器的数据由D引脚输入、Q引脚输出,每次移位脉冲引脚(SHCP)提供一个时钟脉冲,D引脚的数据就会输出并保存到Q引脚上。由图可见,移位脉冲引脚(SHCP)是与8个移位寄存器直接相连的,故每给一个移位脉冲信号,全部8个移位寄存器均会执行相同操作:数据由D引脚向Q引脚移一位。值得注意的是,移位寄存器的数据来源为数据串行输入引脚(DS),故在每次给移位脉冲信号之前,我们需要准备好该引脚的值。特别地,依次给出8个移位脉冲信号后,可将1字节数据完整移入8个移位寄存器中,且该字节的8个bit位将会依次分布在8个移位寄存器的Q引脚上,实现对1字节数据的输入操作。

该芯片的8个存储寄存器均为锁存寄存器,每给一个锁存脉冲信号,8个存储寄存器的Q引脚就会向外并行输出数据并锁存D引脚上的数据。特别地,当移位寄存器完成1字节数据的输入操作后,此时给一个锁存脉冲信号,可实现将该字节数据在Q0~Q7引脚上的并行输出操作。

使用方法小结:

- 将要准备输入的位数据移入芯片的数据输入引脚DS;

- 在移位脉冲信号下,DS引脚上的位数据将被逐位移入移位寄存器中;

- 在锁存脉冲信号下,将已移入移位寄存器中数据送入存储寄存器中,实现并行输出;

值得注意的是,移位脉冲(移入数据)与锁存脉冲(输出数据)是两个相互独立的过程,实际应用时互不干扰,即可在输出数据的同时移入数据。