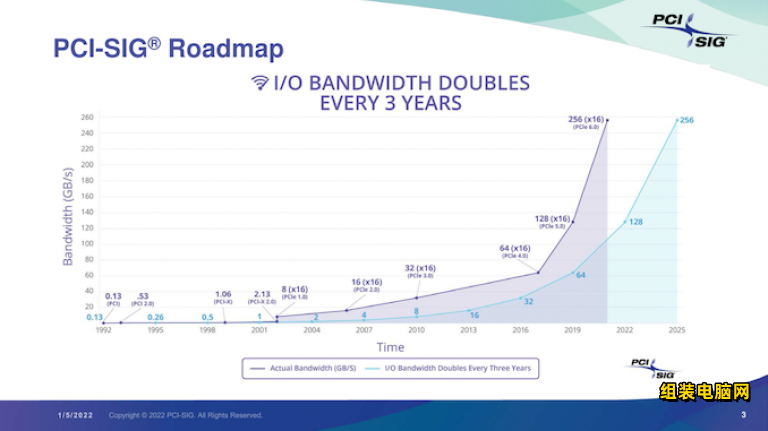

眼看Intel才刚为新一代处理器加入PCIe 5.0通道的支持,至今也未见到到相关的设备投入市场,但负责制定PCIe通道规范的PCI-SIG(周边元件互连特别兴趣小组)就已经在早早在预备下一代的标准,并在近日正式决定了PCIe 6.0的相关特色。

PCI-SIG表示,现在的通道速度成长速率大约维持着每隔三年就翻倍一次的周期,而他们很荣幸的能够在PCIe 5.0规范推出后的三年内就完成了下一代PCIe 6.0的设计,新的PCIe 6.0通道将继续着重在更具经济效益的扩展解决方案,为数据中心、人工智慧学习、物联网、自动设备等领域产生重大的影响,同时也兼具了“向下相容”的特性,保护之前的投资不会因此白费。

PCIe规范以约每3年的时间完成频宽翻倍的迭代。

PCIe规范以约每3年的时间完成频宽翻倍的迭代。新的PCIe 6.0在设计上有以下几个特点:

1、比PCIe 5.0通道高出2倍的频宽,达到64 GT/s原始资料传输速度,相当于在x16接口下的传输量达256 GB/s

2、支持PAM4(四阶脉冲振幅调变)信号传输,与业界现有的PAM4标准兼容。

3、支持FEC(Lightweight Forward Error Correct)、CRC(Cyclic Redundancy Check)校正功能,减少PAM4传输上的错误机率

4、基于Flit (flow control unit)的编码将能够支持PAM4调变,并FEC、CRC相结合,实现两倍的频宽。

5、更新Flit模式下的数据布局,以此提供更多功能并简化处理。

6、可以兼容过去的PCIe通道。

以PCIe 6.0的频宽换算,x1通道就达到了16 GB/s之多,直接等于了PCIe3.0x16的频宽,如此巨大的频宽对于企业级应用来说自然是最喜闻乐见,不过这个规范就目前只能算得上超前部署,要能够实际应用,还是得等到A、I两家处理器厂正式导入其支持功能且有相关周边的推出才算数,以目前PCIe 5.0才在刚预热的阶段来看,快的话可能也要再等个4、5年才有机会了。