AMD官方已经披露了Zen4架构的规划,包括消费级的锐龙、服务器的霄龙,都是5nm制程。Zen4产品在桌面处理器产品命名为锐龙 7000系列(Raphael),新的AM5 LGA1718封装插槽,支持双通道DDR5、PCIe 5.0,下半年发布。

在服务器端则是霄龙7004系列(Genoa),新的SP5 LGA6096封装插槽,最多96核心192线程,支持12通道DDR5、128条PCIe 5.0,下半年登场。

还有个衍生版Zen4c(Bergamo),针对云端服务最佳化,最多128核心256线程,明年初推出。

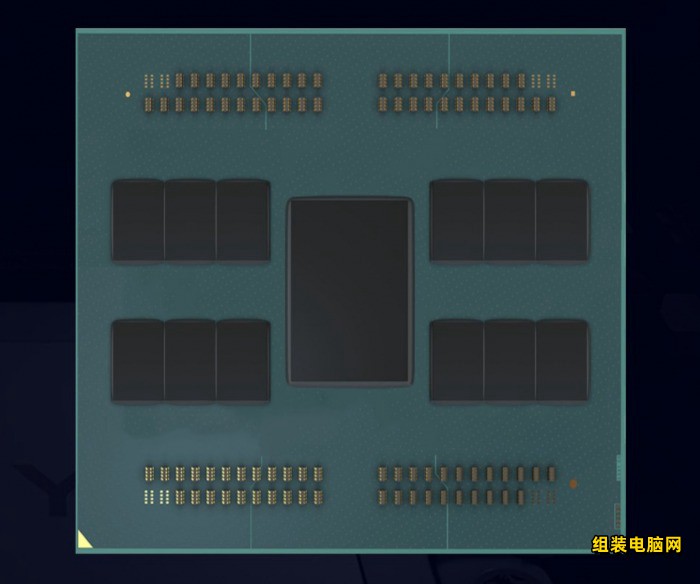

日前我们曾见过一张Zen4 霄龙的图片,但只有正面。现在新的霄龙图片来了,正反面都有。

事实上,SP5接口的针脚/触点定义、安装支架结构,早在去年就随着某厂商被洩露了。

这颗样品是入门的16核心32线程,最高加速频率3.7GHz,热设计功耗195W,但是这只是样品规格,不代表最终SKU。

更有趣的是,同时爆出的还有X光下的照片,可以看到内部三颗芯片:居中大的是负责输入输出的IOD,左右各有一颗CCD,显然每颗只有8个核心。

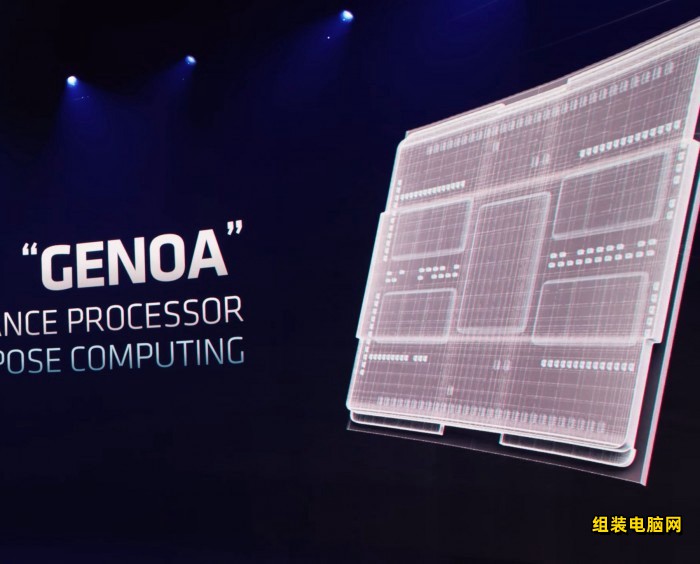

如果要凑够96个核心,那就得12颗CCD,这和AMD先前公布的示意图布局完全相符。

相比 7纳米制程,5纳米制程的 EPYC 处理器晶体管数量增长一倍,能耗只有 7纳米一半。代号 Genoa 的 EPYC 服务器处理器拥有最多 96 个 Zen 4 架构核心,并支持 DDR5 和 PCI-E 5.0,以及允许设备保持一致内存连续性的 CXL 1.1 接口,目标市场是以高性能运算 (HPC)、数据中心、企业和云端运算工作负载,预计 2022 年推出。