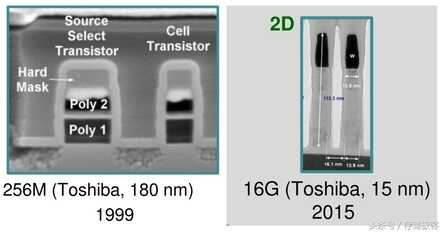

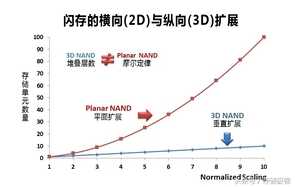

1999年在东芝180nm下制造出256MB容量的闪存,2015年在15nm制程下闪存单Die容量提升了64倍达到16GB。和摩尔定律晶体管数量每18-24个月翻一番的理论相比,闪存容量的提升速度已经落后了。

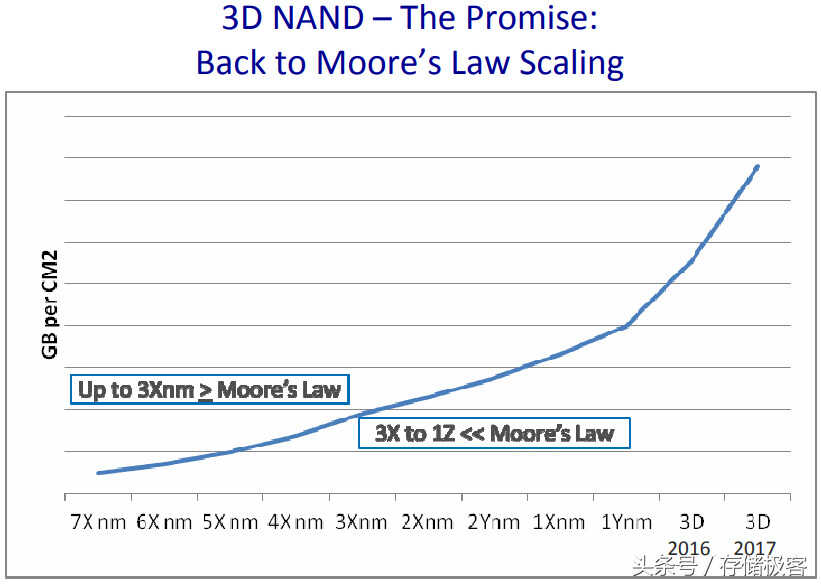

2014年的闪存峰会上,美光说3D闪存能将闪存带回摩尔定律的路线上来,不过现在来看基本已经失败了:闪存不仅没有因3D制程应用而大幅降价,反而掀起了一波涨价潮。

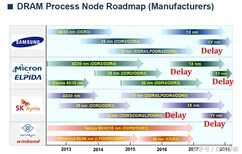

其实遇到问题的不仅仅是NAND闪存,包括DRAM内存也遇到同样技术瓶颈,各大原厂更新制程的进度普遍低于预期,各种延期成了家常便饭。

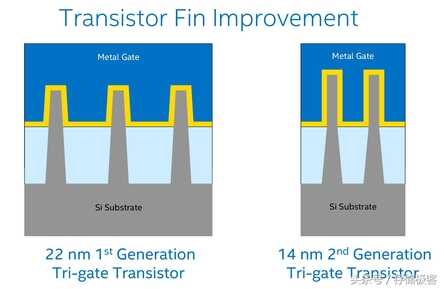

英特尔在14nm这个制程节点上已经停留了3代,一直是修修补补的状态,迟迟拿不出10nm芯片。平面闪存方面,东芝已经发展到15nm制程,SK Hynix为14nm,基本都和当代CPU制程持平。

更先进的制程(10nm~3nm)需要EUV极紫外光刻的支持,而EUV技术花了很多年直到现在刚在实验室条件下达到适合应用量产的水平。使用EUV光刻的新设备成本高昂的同时,工作状态比当前氩氟雷射耗费10倍以上电能。由于EUV光刻的能源转换效率只有0.02%左右,一台输出功率250瓦的EUV光刻机每天会消耗3万度电。对于EUV光刻,台积电曾表示希望未来制程工艺中越少用到越好,因为实在是太贵了!

既然制程升级空间小,那么2D向3D转换成效如何?2D闪存时代通过制程升级可以获得近似指数级增长,而3D时代则只会有线性的增加,因为从原理上来说3D做的是垂直方向上的堆叠,而不是2D闪存制程升级时在长宽尺寸上的同时进步。3D闪存的确是未来的发展方向,但却不是万能的救世主。

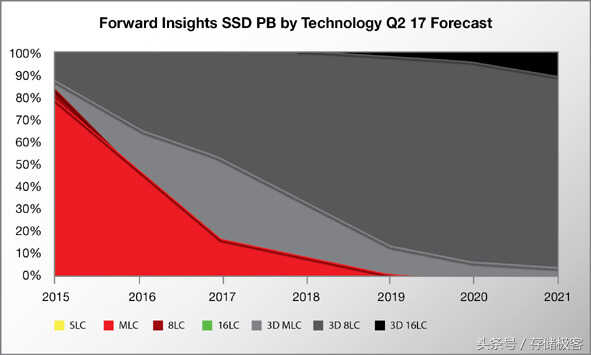

不管如何,在制程微缩渐入瓶颈的状况下3D工艺还是能做出一些成本上的改善,尤其是64层以上的3D堆叠闪存:东芝在2007年就首次宣布3D闪存,直到今年投入大规模使用的正是64层堆叠技术。

除了将原有的Fab 2与Fab 5升级为3D工艺外,东芝还计划新建Fab 6:新工厂从一开始就将以3D闪存制造为目标。

除了3D堆叠之外,未来能让闪存真正降价的方向还有QLC:东芝64层堆叠的BiCS Gen 3闪存量产后很快又宣布了96层 BiCS 4闪存以及3D QLC技术。

相比3D堆叠,其实QLC对于降成本更为靠谱,当然前提是要有过硬的技术解决寿命问题:作为闪存发明者,东芝首个宣布QLC也是非常有底气的。

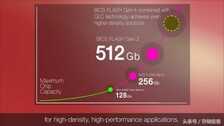

借助于更高的堆叠层数以及QLC每个存储单元多出的1bit存储能力,东芝能将当前最大512Gb的闪存单Die容量提升至768Gb。如果使用16die封装,单个闪存颗粒就能拥有1.5TB存储容量!东芝还承诺3D QLC将提供1000次以上擦写寿命,几乎等同于现在的TLC闪存,而且不会让大家等太久:大约明年晚些时候就会出现。

可能有玩家还会联想到Intel与美光联合开发的3D XPoint,不过它主要面向的是高性能领域,不差钱的企业级应用也许会用的上它,而容量为王的消费级固态硬盘当中,英特尔16G傲腾内存(缓存盘)的失败大家都已经看到了3D XPoint不会对降价有任何帮助。