自从去年开始,以ChatGPT为代表的生成式AI(Generative)站在了整个世界的聚光灯下。ChatGPT可以理解用户基于自然语言的输入,并且产生相应的输出。ChatGPT基于大语言模型技术,通过使用海量的语料训练,可以实现回答用户的各种问题,还可以帮助用户完成一些简单的任务,包括完成文档编写甚至Python代码编写等等。

而在五月十日,谷歌在IO大会上发布了ChatGPT的竞品,即PaLM 2大语言模型。谷歌表示,目前ChatGPT类生成式大语言模型最重要的用户体验之一就是帮助用户编写代码,而PaLM 2的一大特性就是完成20多种编程语言的支持。其中,对于芯片设计工程师来说,最大的亮点就是PaLM 2支持数字电路设计领域最常用的编程语言Verilog。

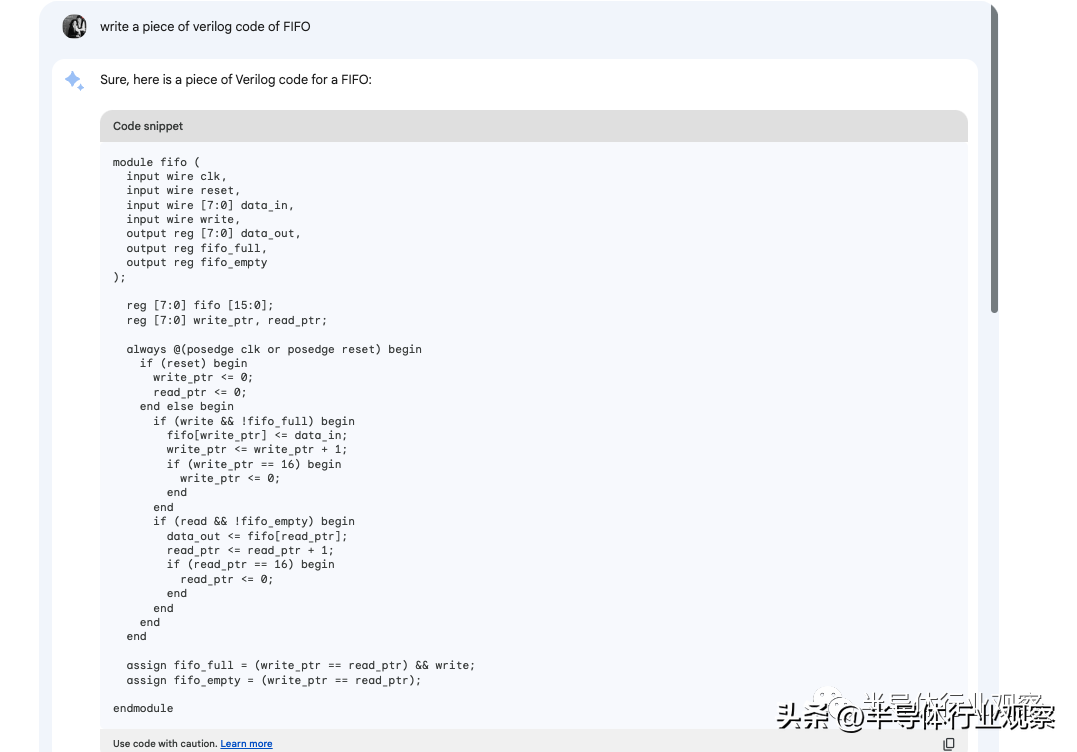

百闻不如一试,目前PaLM 2已经在谷歌的Bard平台上线开放公测,因此我们也尝试使用Bard去体会了一把PaLM 2生成Verilog代码的能力。在试验中,我们让Bard生成了两段代码,一段代码是生成一个FIFO(数字电路中最常用的模块之一),而另一段代码则是生成一个模块,其中包含了两个前面编写的FIFO,并且让第一个FIFO的输出接入第二个FIFO的输入。生成的方法非常简单,我们只需要给Bard一个基于自然语言的指令(prompt),Bard就能够在几秒钟之内完成相应的代码生成。例如,在第一个实验中,我们使用的指令是“生成一段Verilog代码来实现FIFO”,生成结果如下图:

从结果来看该生成的代码的语法正确,逻辑基本正确,但是在FIFO full和empty的信号逻辑上并没有完全弄对(当然其实FIFO的full和empty的逻辑也是面试中常考的问题,要完全弄对并没那么简单)。在代码风格上,我们还可以在指令中加入更多提示,类似“在代码中加入更多注释”,“使用参数来定义接口宽度”等等。

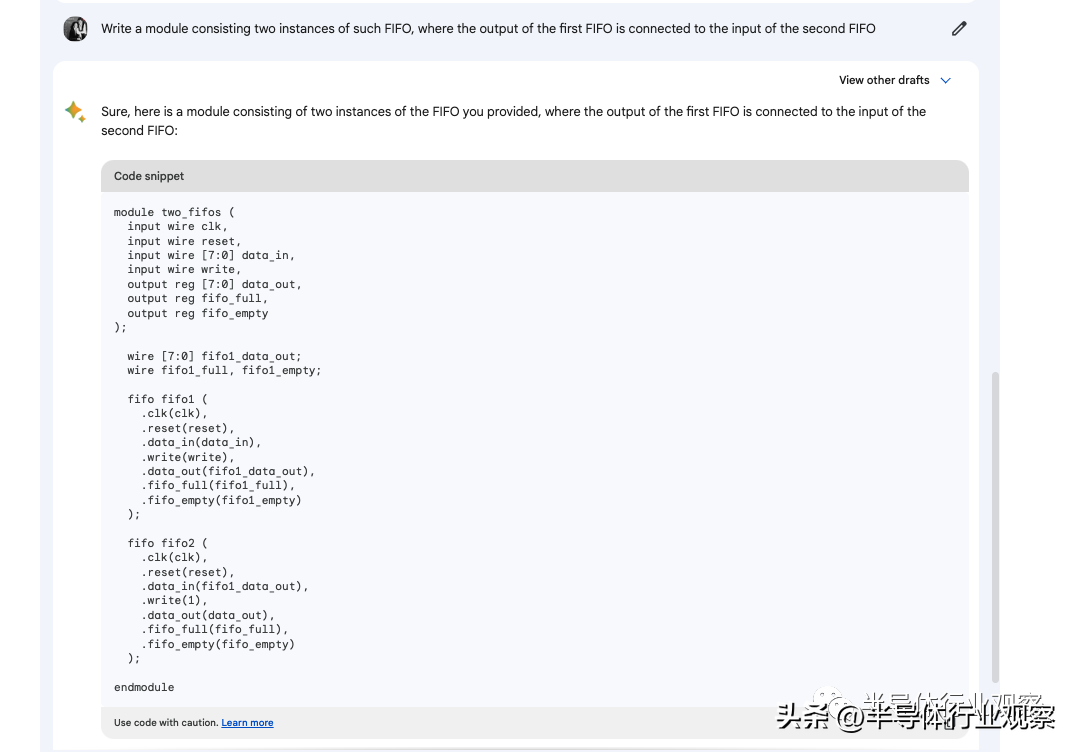

而在第二个实验中,我们主要看的是Bard能否复用之前生成的模块,并且基于这个来生成新的更大的模块。我们使用的指令是“写一个模块,其中包括两个你前面写的FIFO模块,并且第一个FIFO的输出接入第二个FIFO的输入”。

在这里我们可以看到生成的代码基本正确,因此我们认为PaLM 2基本拥有了能基于自底向上生成复杂代码的能力。

芯片设计领域生成式AI的进化之路

我们从上述实验中可以看到,谷歌的PaLM 2已经具有了基本的Verilog代码生成能力,可以生成基本模块和复合模块,当然其代码生成的质量还有待提高。而除了PaLM 2之外,我们认为其他公司推出的类似ChatGPT的大语言模型也有可能会加入对于Verilog类硬件描述语言的支持。

根据谷歌在IO大会上发布的信息,目前ChatGPT类的大语言模型已经成为许多工程师在代码编写时的重要助手。如果我们参考IT领域软件开发工程师应用ChatGPT类大语言模型协助代码编写的发展的话,我们认为在芯片行业大语言模型也非常有可能会起到重要作用。这里,根据大语言模型在开发流程中起到的角色,我们可以大致分成三种应用。第一种应用是根据用户的指令直接生成代码,即我们在本文前面给出的两个例子。第二种应用是在工程师编写代码的时候,帮助工程师自动补全代码;例如工程师只需要输入一行代码的前几个字符,大语言模型就可以根据代码的上下文自动帮助补全代码,从而节省工程师的开发时间。第三种应用是帮助工程师分析代码和debug,正如ChatGPT可以帮助用户优化Python代码并找到代码中的bug一样,经过相关数据训练的大语言模型也可以在Verilog中实现相似的功能。

展望未来,参考大语言模型在IT行业的应用轨迹,我们认为大语言模型对于芯片设计方面的帮助预计将会从代码自动补全开始,因为这也是大语言模型在IT行业的切入口——目前我们已经看到类似Github co-pilot这样的代码补全产品已经得到了许多IT公司的应用来帮助软件工程师提升编程效率。相对来说,代码补全类应用对于大语言模型的要求相对较低,目前的模型已经能实现相当高的准确率,因此我们预期在芯片设计领域也会有应用在Verilog领域的基于大语言模型的代码补全工具会很快出现帮助工程师提高效率(估计谷歌内部芯片团队已经开始使用类似的工具)。

在代码补全之后,随着大语言模型的进一步发展,根据用户的指令自动生成代码的大语言模型也将会得到越来越多的应用。这类代码直接生成类应用从目前来看还需要和整个项目开发流程进一步磨合——究竟这类代码自动生成的应用最适合使用在底层模块的编写,还是在上层模块间集成的生成上,还需要进一步探索,但是无论如何ChatGPT在自动代码编写领域的潜力惊人,可以把原来人工需要数小时才能编写完的代码在几秒内完成,这样的效率提升无疑将会给整个行业和芯片开发流程带来革命性的变化。

目前来看,ChatGPT类大语言模型在Python等流行编程语言的代码编写方面已经有很不错的效果,这证明了大语言模型实现自动代码编写、补全和debug在理论和工程上都是可以实现的。谷歌的PaLM 2对于Verilog的支持仍然有待进一步完善的主要原因我们认为还是训练的数据量不够。从训练数据数量的角度来说,互联网上有海量的开源Python代码可供训练大语言模型来完成高质量的代码生成,但是互联网上可用于训练大语言模型的Verilog代码的数量比起Python等流行语言来说可能是要少了几个数量级。并不是人类编写的Verilog代码数量不够多,而是绝大多数Verilog代码都不是开源的,而是芯片公司的知识产权,例如谷歌在训练PaLM的时候不太可能获得高通的Verilog代码。未来谁会在开发芯片设计领域的大语言模型方面拔得头筹?我们认为有几个不可忽视的力量:

首先是拥有全栈技术能力的大型技术公司,这些公司既有开发大语言模型的能力,又有成功的芯片业务,包括美国的谷歌和中国的华为等。从技术上来说,这些公司积累了大量的Verilog相关代码可供训练大语言模型,而从业务上来说,这些公司同样也有使用大语言模型来提升芯片设计团队效率的驱动力。

其次是EDA巨头,包括Synopsys、Cadence等。这些EDA公司拥有极强的业务驱动力和紧迫感,因为大语言模型AI确实会成为EDA行业下一个革命性变化,谁在这个领域占领了先机就会在下一代EDA竞争中取得优势;从技术积累上来说,这些公司拥有不错的AI模型能力,同时也有海量的Verilog代码数据量可供训练模型(因为这些EDA公司都有相当成功的IP业务,在开发这些IP的同时积累了足够的高质量代码数据)。

最后,开源社区的力量也不容忽视。从大语言模型角度来看,开源社区在CahtGPT以及开源LLAMA语言模型的基础上做了大量有意义的探索,另外随着RISC-V等开源项目的增加,开源社区拥有的数据量也会越来越多。我们预期开源社区有机会去实现一些小而美的基于大语言模型的新颖应用,从而也能推动整个大语言模型在芯片设计领域的技术发展。

生成式AI会如何影响芯片设计工程师的工作

那么,随着ChatGPT式AI在芯片设计中扮演越来越重要的角色,芯片工程师的日常工作将会发生怎么样的变化?由于这里ChatGPT类生成式AI主要针对代码编写等前端工作,我们这里的讨论范围也主要是前端数字设计工程师。

首先,对于主要工作是前端模块设计和集成的芯片工程师来说,我们预计很快就会有ChatGPT类的工具可以帮助代码补全,从而增加效率。而在未来三到五年的时间范围内,直接使用ChatGPT类生成式AI首先模块代码编写有望获得真正的应用。从这个角度来说,我们并不认为前端工程师的工作会被取代;相反,数字前端工程师的工作可能会越来越多地专注于模块的功能定义,以及如何使用生成式AI能理解的方式来描述这个设计,让AI能产生和工程师设计相符的代码;从这个角度,甚至可能会出现一些标准化的模块功能定义描述语言,从而让AI能产生合理的代码。

此外,芯片验证工程师的工作将会变得越来越重要。生成式AI可以在几秒钟内生成代码,但是其生成质量从目前来看尚需提高。从这个角度,芯片验证一方面需要确保AI生成的代码没有bug,而更重要的是,芯片验证需要能和代码生成形成闭环,例如如何实现一套工作流程,让AI生成的代码可以快速使用testbench来确保功能是否正确,并且有办法告诉AI哪里功能不对来提示AI修改,从而在经过多次迭代后能让AI自动生成正确的代码。虽然可能会需要多次迭代,但是因为每次代码生成需要的时间很短,因此总得来看需要的代码生成时间还是比起手写要快许多。此外,使用生成式AI来自动生成testbench以及验证需要的assertion也将会改变验证工程师的工作流程,工程师将会需要花更多时间教会AI来生成正确的代码,从而大大提升效率。